## PROGRAMMABLE TIMER

- 24 FLIP-FLOP STAGES COUNTS FROM 2<sup>0</sup>

TO 2<sup>24</sup>

- LAST 16 STAGES SELECTABLE BY BCD SELECT CODE

- GROUP SELECT INDICATES ONE OR MORE PRIORITY INPUTS

- QUIESCENT CURRENT SPECIFIED UP TO 20V

- STANDARDIZED SYMMETRICAL OUTPUT CHARACTERISTICS

- 5V, 10V AND 15V PARAMETRIC RATINGS

- INPUT LEAKAGE CURRENT I<sub>I</sub> = 100nA (MAX) AT V<sub>DD</sub> = 18V T<sub>A</sub> = 25°C

- 100% TESTED FOR QUIESCENT CURRENT

- MEETS ALL REQUIREMENTS OF JEDEC JESD13B "STANDARD SPECIFICATIONS FOR DESCRIPTION OF B SERIES CMOS DEVICES"

### **DESCRIPTION**

HCF4536B is a monolithic integrated circuit fabricated in Metal Oxide Semiconductor technology available in DIP package.

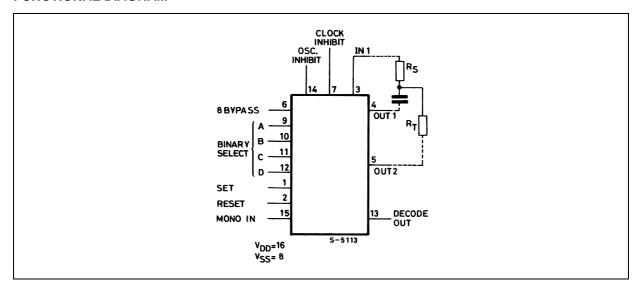

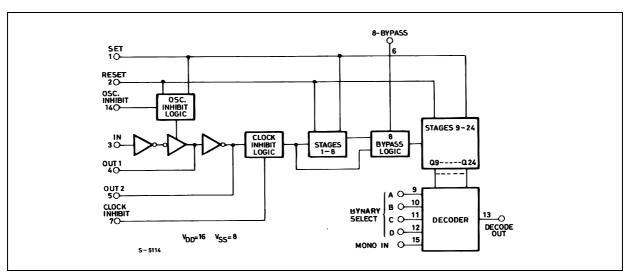

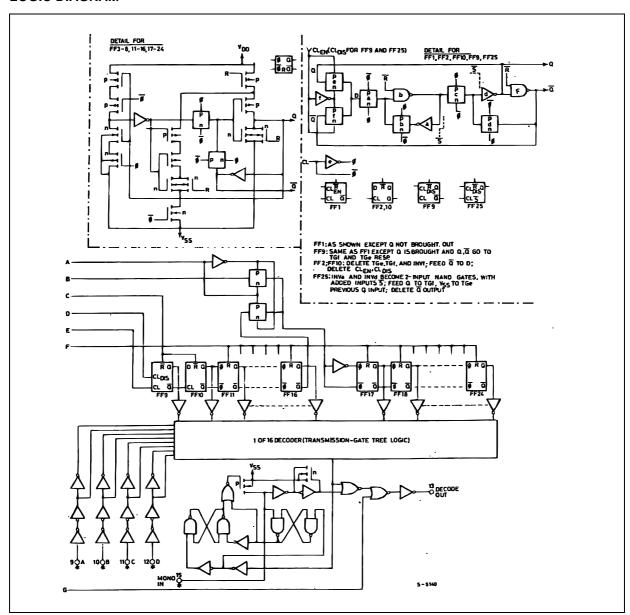

HCF4536B is a programmable timer consisting of 24 ripple-binary counter stages. The salient feature of this device is its flexibility. The device can count from 1 to 2<sup>24</sup> or the first 8 stages can be bypassed to allow an output, selectable by a 4-bit code, from any one of the remaining 16 stages. It

#### **ORDER CODES**

| PACKAGE | TUBE       | T & R |

|---------|------------|-------|

| DIP     | HCF4536BEY |       |

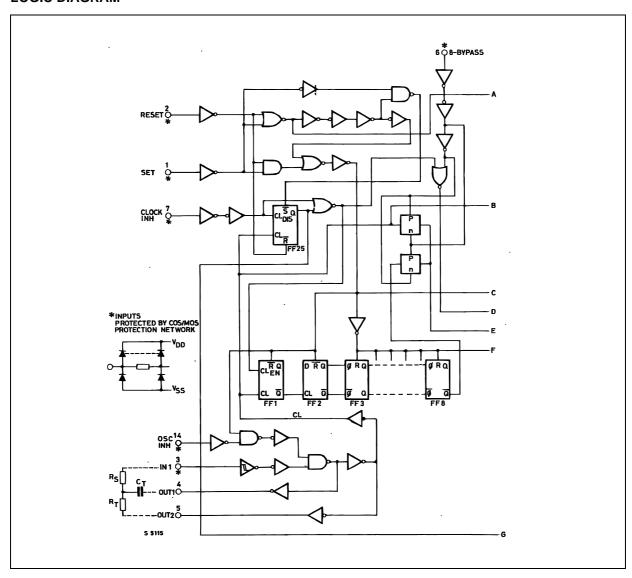

can be driven by an external clock or an RC oscillator that can be constructed using on-chip components. Input IN1 serves as either the external clock input or the input to the on-chip RC oscillator. OUT1 and OUT2 are connection terminals for the external RC components. In addition, an on-chip monostable circuit is provided to allow a variable pulse width output. Various timing functions can be achieved using combinations of these capabilities. A logic "1" on the 8-BYPASS input enables a bypass of the first 8 stages and makes stage 9 the first counter stage of the last 16 stages. Selection of 1 of 16 outputs is accomplished by the decoder and the BCD inputs A, B, C, and D. MONO IN is the timing input

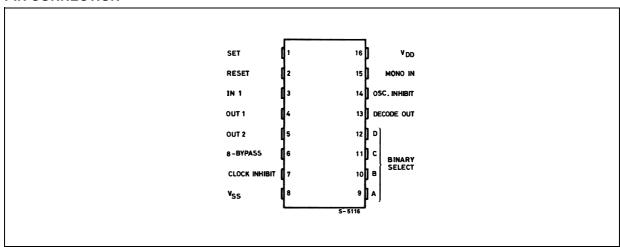

#### **PIN CONNECTION**

October 2002 1/13

for the on-chip monostable oscillator. Grounding of the MONO IN terminal through a resistor of 10  $K\Omega$  or higher, disables the one shot circuit and connects the decoder directly to the DECODE OUT terminal. A resistor to  $V_{DD}$  and a capacitor to ground from the MONO IN terminal enables the

one-shot circuit and controls its pulse width. A fast test mode is enabled by a logic "1" on 8-BYPASS, SET, and RESET. This mode divides the 24-stage counter into three 8-stage sections to facilitate a fast test sequence.

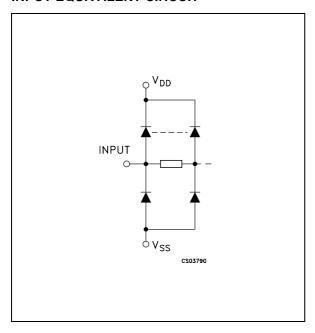

#### **INPUT EQUIVALENT CIRCUIT**

#### **PIN DESCRIPTION**

| PIN No        | SYMBOL           | NAME AND FUNCTION                           |

|---------------|------------------|---------------------------------------------|

| 9, 10, 11, 12 | A, B, C, D       | Binary Select Input                         |

| 1             | SET              | Set input                                   |

| 2             | RESET            | Reset Input                                 |

| 15            | MONO IN          | Monostable OscillatorTiming Input           |

| 6             | 8BYPASS          | 8Bypass input( bypass the first 8 stages)   |

| 3             | IN1              | External Clock Input or RC oscillator Input |

| 4, 5          | OUT1, OUT2       | Outputs                                     |

| 13            | DECODE<br>OUT    | Decode Out Terminal                         |

| 7             | CLOCK<br>INHIBIT | Clock Inhibit Input                         |

| 14            | OSC.<br>INHIBIT  | Oscillator Inhibit Input                    |

| 8             | V <sub>SS</sub>  | Negative Supply Voltage                     |

| 16            | $V_{DD}$         | Positive Supply Voltage                     |

#### **FUNCTIONAL DIAGRAM**

### **TRUTH TABLE**

| ln1 | Set | Reset | Clock Inh | Osc. Inh | Out1 | Out2 | Decode Out            |

|-----|-----|-------|-----------|----------|------|------|-----------------------|

|     | L   | L     | L         | L        | 7    | 7    | No Change             |

|     | L   | L     | L         | L        | 7    | 7    | Advance to Next State |

| Х   | Н   | L     | L         | L        | L    | Н    | Н                     |

| Х   | L   | Н     | L         | L        | L    | Н    | L                     |

| Х   | L   | L     | Н         | L        |      |      | No Change             |

| L   | L   | L     | L         | Х        | L    | Н    | No Change             |

| Н   | L   | L     | L         |          | 7_   |      | Advance to Next State |

X : Don't Care

### **DECODE OUT SELECTION TABLE**

| D | С | В | Α. | NUMBER OF STAGE | S IN DIVIDER CHAIN |

|---|---|---|----|-----------------|--------------------|

| ט | C | В | Α  | 8-BYPASS = 0    | 8-BYPASS = 1       |

| L | L | L | L  | 9               | 1                  |

| L | L | L | Н  | 10              | 2                  |

| L | L | Н | L  | 11              | 3                  |

| L | L | Н | Н  | 12              | 4                  |

| L | Н | L | L  | 13              | 5                  |

| L | Н | L | Н  | 14              | 6                  |

| L | Н | Н | L  | 15              | 7                  |

| L | Н | Н | Н  | 16              | 8                  |

| Н | L | L | L  | 17              | 9                  |

| Н | L | L | Н  | 18              | 10                 |

| Н | L | Н | L  | 19              | 11                 |

| Н | L | Н | Н  | 20              | 12                 |

| Н | Н | L | L  | 21              | 13                 |

| Н | Н | L | Н  | 22              | 14                 |

| Н | Н | Н | L  | 23              | 15                 |

| Н | Н | Н | Н  | 24              | 16                 |

#### **BLOCK DIAGRAM**

## **LOGIC DIAGRAM**

#### **LOGIC DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                               | Value                         | Unit |

|------------------|-----------------------------------------|-------------------------------|------|

| V <sub>DD</sub>  | Supply Voltage                          | -0.5 to +22                   | V    |

| VI               | DC Input Voltage                        | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| lį               | DC Input Current                        | ± 10                          | mA   |

| P <sub>D</sub>   | Power Dissipation per Package           | 200                           | mW   |

|                  | Power Dissipation per Output Transistor | 100                           | mW   |

| T <sub>op</sub>  | Operating Temperature                   | -55 to +125                   | °C   |

| T <sub>stg</sub> | Storage Temperature                     | -65 to +150                   | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All voltage values are referred to V<sub>SS</sub> pin voltage.

### **RECOMMENDED OPERATING CONDITIONS**

| Symbol          | Parameter             | Value                | Unit |

|-----------------|-----------------------|----------------------|------|

| $V_{DD}$        | Supply Voltage        | 3 to 20              | V    |

| V <sub>I</sub>  | Input Voltage         | 0 to V <sub>DD</sub> | V    |

| T <sub>op</sub> | Operating Temperature | -55 to 125           | °C   |

### **DC SPECIFICATIONS**

|                 | Test Condition Value     |      |                  |             |                       |       |                   |      |        |       |       |      |      |

|-----------------|--------------------------|------|------------------|-------------|-----------------------|-------|-------------------|------|--------|-------|-------|------|------|

| Symbol          | Parameter                | VI   | VI VO IIOI VDD A |             | T <sub>A</sub> = 25°C |       | -40 to 85°C       |      | -55 to | 125°C | Unit  |      |      |

|                 |                          | (V)  | (V)              | <b>(μA)</b> | . ^ \                 | Min.  | Тур.              | Max. | Min.   | Max.  | Min.  | Max. |      |

| ΙL              | Quiescent Current        | 0/5  |                  |             | 5                     |       | 0.04              | 5    |        | 150   |       | 150  |      |

|                 |                          | 0/10 |                  |             | 10                    |       | 0.04              | 10   |        | 300   |       | 300  | μA   |

|                 |                          | 0/15 |                  |             | 15                    |       | 0.04              | 20   |        | 600   |       | 600  | μΑ   |

|                 |                          | 0/20 |                  |             | 20                    |       | 0.08              | 100  |        | 3000  |       | 3000 |      |

| V <sub>OH</sub> | High Level Output        | 0/5  |                  | <1          | 5                     | 4.95  |                   |      | 4.95   |       | 4.95  |      |      |

|                 | Voltage                  | 0/10 |                  | <1          | 10                    | 9.95  |                   |      | 9.95   |       | 9.95  |      | V    |

|                 |                          | 0/15 |                  | <1          | 15                    | 14.95 |                   |      | 14.95  |       | 14.95 |      |      |

| V <sub>OL</sub> | Low Level Output         | 5/0  |                  | <1          | 5                     |       | 0.05              |      |        | 0.05  |       | 0.05 |      |

|                 | Voltage                  | 10/0 |                  | <1          | 10                    |       | 0.05              |      |        | 0.05  |       | 0.05 | V    |

|                 |                          | 15/0 |                  | <1          | 15                    |       | 0.05              |      |        | 0.05  |       | 0.05 |      |

| $V_{IH}$        | High Level Input         |      | 0.5/4.5          | <1          | 5                     | 3.5   |                   |      | 3.5    |       | 3.5   |      |      |

|                 | Voltage                  |      | 1/9              | <1          | 10                    | 7     |                   |      | 7      |       | 7     |      | V    |

|                 |                          |      | 1.5/13.5         | <1          | 15                    | 11    |                   |      | 11     |       | 11    |      |      |

| $V_{IL}$        | Low Level Input          |      | 4.5/0.5          | <1          | 5                     |       |                   | 1.5  |        | 1.5   |       | 1.5  |      |

|                 | Voltage                  |      | 9/1              | <1          | 10                    |       |                   | 3    |        | 3     |       | 3    | V    |

|                 |                          |      | 13.5/1.5         | <1          | 15                    |       |                   | 4    |        | 4     |       | 4    |      |

| I <sub>OH</sub> | Output Drive             | 0/5  | 2.5              | <1          | 5                     | -1.36 | -3.2              |      | -1.1   |       | -1.1  |      |      |

|                 | Current                  | 0/5  | 4.6              | <1          | 5                     | -0.44 | -1                |      | -0.36  |       | -0.36 |      | mA   |

|                 |                          | 0/10 | 9.5              | <1          | 10                    | -1.1  | -2.6              |      | -0.9   |       | -0.9  |      | IIIA |

|                 |                          | 0/15 | 13.5             | <1          | 15                    | -3.0  | -6.8              |      | -2.4   |       | -2.4  |      |      |

| I <sub>OL</sub> | Output Sink              | 0/5  | 0.4              | <1          | 5                     | 0.44  | 1                 |      | 0.36   |       | 0.36  |      |      |

|                 | Current                  | 0/10 | 0.5              | <1          | 10                    | 1.1   | 2.6               |      | 0.9    |       | 0.9   |      | mΑ   |

|                 |                          | 0/15 | 1.5              | <1          | 15                    | 3.0   | 6.8               |      | 2.4    |       | 2.4   |      |      |

| I <sub>I</sub>  | Input Leakage<br>Current | 0/18 | Any In           | put         | 18                    |       | ±10 <sup>-5</sup> | ±0.1 |        | ±1    |       | ±1   | μΑ   |

| C <sub>I</sub>  | Input Capacitance        |      | Any In           | put         |                       |       | 5                 | 7.5  |        |       |       | _    | pF   |

The Noise Margin for both "1" and "0" level is: 1V min. with  $V_{DD}$ =5V, 2V min. with  $V_{DD}$ =10V, 2.5V min. with  $V_{DD}$ =15V

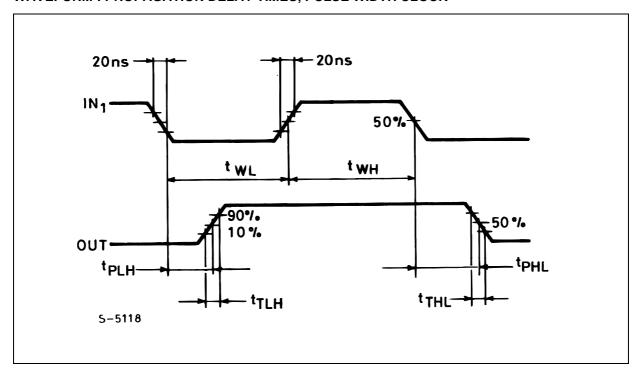

# $\textbf{DYNAMIC ELECTRICAL CHARACTERISTICS} \; (\textbf{T}_{amb} = 25^{\circ} \textbf{C}, \;\; \textbf{C}_{L} = 50 \text{pF}, \; \textbf{R}_{L} = 200 \text{K}\Omega, \;\; \textbf{t}_{f} = \textbf{t}_{f} = 20 \; \text{ns})$

|                                   |                          |                     | Test Condition | ,    | /alue (* | <b>'</b> ) | Unit |

|-----------------------------------|--------------------------|---------------------|----------------|------|----------|------------|------|

| Symbol                            | Parameter                | V <sub>DD</sub> (V) |                | Min. | Тур.     | Max.       |      |

| t <sub>PLH</sub> t <sub>PHL</sub> | Propagation Delay Time   | 5                   |                |      | 1        | 2          |      |

|                                   | (Clock to Q1, 8-Bypass   | 10                  |                |      | 0.5      | 1          | μs   |

|                                   | High)                    | 15                  |                |      | 0.35     | 0.7        |      |

|                                   | Propagation Delay Time   | 5                   |                |      | 2.5      | 5          |      |

|                                   | (Clock to Q1, 8-Bypass   | 10                  |                |      | 0.8      | 0.6        | μs   |

|                                   | Low)                     | 15                  |                |      | 0.6      | 1.2        |      |

|                                   | Propagation Delay Time   | 5                   |                |      | 4        | 8          |      |

|                                   | (Clock to Q16)           | 10                  |                |      | 1.5      | 3          | μs   |

|                                   |                          | 15                  |                |      | 1        | 2          |      |

|                                   | Propagation Delay Time   | 5                   |                |      | 150      | 300        |      |

|                                   | (Qn to Qn+1)             | 10                  |                |      | 75       | 150        | ns   |

|                                   |                          | 15                  |                |      | 50       | 100        |      |

| t <sub>PLH</sub>                  | Propagation Delay Time   | 5                   |                |      | 300      | 600        |      |

|                                   |                          | 10                  |                |      | 125      | 250        | ns   |

|                                   |                          | 15                  |                |      | 80       | 160        |      |

| t <sub>PHL</sub>                  | Reset to Qn              | 5                   |                |      | 3        | 6          |      |

|                                   |                          | 10                  |                |      | 1        | 2          | μs   |

|                                   |                          | 15                  |                |      | 0.75     | 1.5        | i '  |

| t <sub>THL</sub> t <sub>TLH</sub> | Transition Time          | 5                   |                |      | 100      | 200        |      |

| 1112 1211                         |                          | 10                  |                |      | 50       | 100        | ns   |

|                                   |                          | 15                  |                |      | 40       | 80         |      |

| t <sub>W</sub>                    | Pulse Width Clock        | 5                   |                |      | 200      | 400        |      |

| **                                |                          | 10                  |                |      | 75       | 150        | ns   |

|                                   |                          | 15                  |                |      | 50       | 100        |      |

|                                   | Set                      | 5                   |                |      | 200      | 400        |      |

|                                   |                          | 10                  |                |      | 100      | 200        | ns   |

|                                   |                          | 15                  |                |      | 60       | 120        |      |

|                                   | Reset                    | 5                   |                |      | 3        | 6          |      |

|                                   |                          | 10                  |                |      | 1        | 2          | μs   |

|                                   |                          | 15                  |                |      | 0.75     | 1.5        | i '  |

|                                   | Recovery Time Set        | 5                   |                |      | 2.5      | 5          |      |

|                                   | ,                        | 10                  |                |      | 1        | 2          | μs   |

|                                   |                          | 15                  |                |      | 0.6      | 1.6        | 1    |

|                                   | Reset                    | 5                   |                |      | 3.5      | 7          |      |

|                                   |                          | 10                  |                |      | 1.5      | 3          | μs   |

|                                   |                          | 15                  |                |      | 1        | 2          | 1    |

| t <sub>r,</sub> t <sub>f</sub>    | Clock Input Rise or Fall | 5                   |                |      | l        | 1          |      |

| 1, 1                              | Time                     | 10                  |                | ———  | Jnlimite | d          | μs   |

|                                   |                          | 15                  |                |      |          |            | '    |

| f <sub>CL</sub>                   | Maximum Clock Input      | 5                   |                | 0.5  | 1        |            |      |

| ·OL                               | Frequency                | 10                  |                | 1.5  | 3        |            | MHz  |

|                                   | •                        |                     |                | 1    |          | 1          |      |

<sup>(\*)</sup> Typical temperature coefficient for all V<sub>DD</sub> value is 0.3 %/°C.

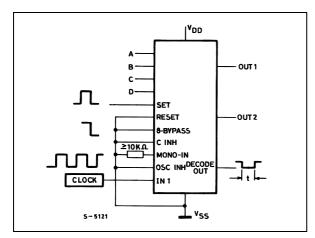

#### **TYPICAL APPLICATIONS**

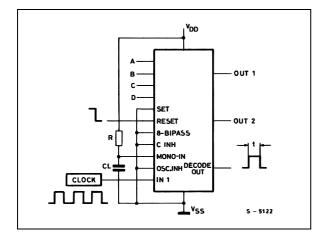

Time Internal Configuration Using External Clock; Set and Clock Inhibit Functions

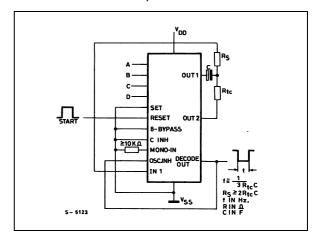

Time Internal Configuration Using Ext. Ck; Reset and Output Monostable to Achieve a Pulse Out

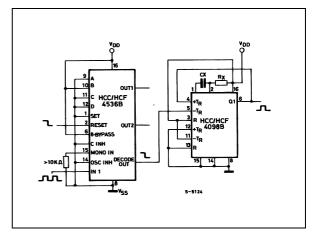

Time Internal Configuration Using On-Chip RC oscillator and Reset Input to Initiate Time Interval

Use of HCF4098B and HCF4536B to get Decode Pulse 8 Clock Pulses after Reset Pulses

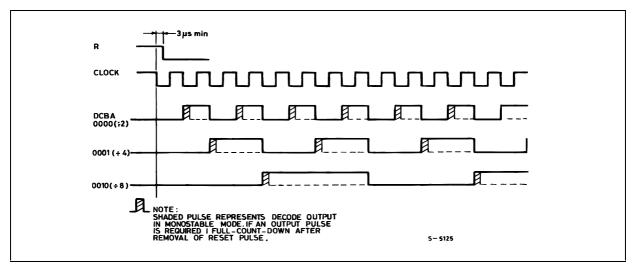

### **TIMING DIAGRAM**

|      | FUNCTIONAL TEST SEQUENCE |       |          |                              |                                                                                                                                     |  |  |  |  |  |  |

|------|--------------------------|-------|----------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|      | Inp                      | uts   |          | Outputs                      | COMMENTS                                                                                                                            |  |  |  |  |  |  |

| In 1 | Set                      | Reset | 8-Bypass | Decade Out<br>Q1 Thru<br>Q24 | All 24 steps are in reset mode                                                                                                      |  |  |  |  |  |  |

| Н    | L                        | Н     | Н        | L                            | Counter is in three 8-stage section in parallel                                                                                     |  |  |  |  |  |  |

| Н    | Н                        | Н     | Н        | L                            | mode                                                                                                                                |  |  |  |  |  |  |

| L    | Н                        | Н     | Н        | L                            | First "H" to "L" Transition of Clock                                                                                                |  |  |  |  |  |  |

| Н    |                          |       |          |                              | 255 "H" to "L" transitions are clocked in the                                                                                       |  |  |  |  |  |  |

| L    | Н                        | Н     | Н        |                              | counter                                                                                                                             |  |  |  |  |  |  |

| L    | Н                        | Н     | Н        | Н                            | The 255 "H" to "L" Transition                                                                                                       |  |  |  |  |  |  |

| L    | L                        | L     | L        | Н                            | Counter converted back to 24 stages in series mode.  Set and Reset must be connected together and simultaneously go from "H" to "L" |  |  |  |  |  |  |

| Н    | L                        | L     | L        | Н                            | In <sub>1</sub> switches to a "H"                                                                                                   |  |  |  |  |  |  |

| L    | L                        | L     | L        | L                            | Counter Ripples from an all "H" state to an all "L" state                                                                           |  |  |  |  |  |  |

#### **FUNCTIONAL TEST SEQUENCE**

Test function has been included for the reduction of test time required to exercise all 24 counter stages. This test function divides the counter into three 8-stage section and 255 counts are loaded in each of the 8-stage sections in parallel. All

flip-flops are now at a "H". The counter is now returned to the normal 24-steps in series configuration. One more pulse is entered into In1 which will cause the counter to ripple from an all "H" state to an all "L" state.

#### **TEST CIRCUIT**

$C_L$  = 50pF or equivalent (includes jig and probe capacitance)  $R_L$  = 200 $K\Omega$   $R_T$  =  $Z_{OUT}$  of pulse generator (typically 50 $\Omega$ )

## WAVEFORM: PROPAGATION DELAY TIMES, PULSE WIDTH CLOCK

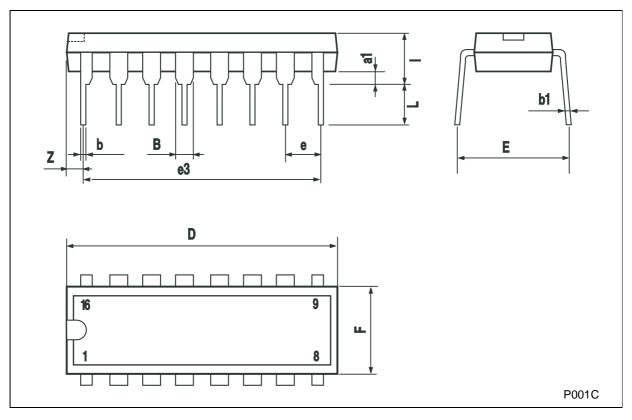

# Plastic DIP-16 (0.25) MECHANICAL DATA

| DIM  |      | mm.   |      | inch  |       |       |  |  |

|------|------|-------|------|-------|-------|-------|--|--|

| DIM. | MIN. | TYP   | MAX. | MIN.  | TYP.  | MAX.  |  |  |

| a1   | 0.51 |       |      | 0.020 |       |       |  |  |

| В    | 0.77 |       | 1.65 | 0.030 |       | 0.065 |  |  |

| b    |      | 0.5   |      |       | 0.020 |       |  |  |

| b1   |      | 0.25  |      |       | 0.010 |       |  |  |

| D    |      |       | 20   |       |       | 0.787 |  |  |

| E    |      | 8.5   |      |       | 0.335 |       |  |  |

| е    |      | 2.54  |      |       | 0.100 |       |  |  |

| e3   |      | 17.78 |      |       | 0.700 |       |  |  |

| F    |      |       | 7.1  |       |       | 0.280 |  |  |

| I    |      |       | 5.1  |       |       | 0.201 |  |  |

| L    |      | 3.3   |      |       | 0.130 |       |  |  |

| Z    |      |       | 1.27 |       |       | 0.050 |  |  |

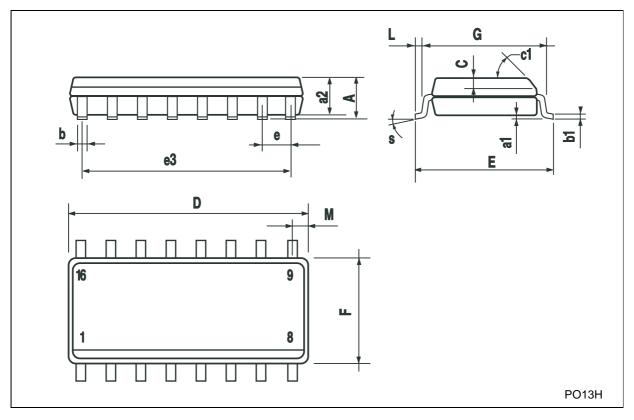

## **SO-16 MECHANICAL DATA**

| DIM  |      | mm.  |       | inch   |       |       |  |

|------|------|------|-------|--------|-------|-------|--|

| DIM. | MIN. | TYP  | MAX.  | MIN.   | TYP.  | MAX.  |  |

| Α    |      |      | 1.75  |        |       | 0.068 |  |

| a1   | 0.1  |      | 0.2   | 0.003  |       | 0.007 |  |

| a2   |      |      | 1.65  |        |       | 0.064 |  |

| b    | 0.35 |      | 0.46  | 0.013  |       | 0.018 |  |

| b1   | 0.19 |      | 0.25  | 0.007  |       | 0.010 |  |

| С    |      | 0.5  |       |        | 0.019 |       |  |

| c1   |      |      | 45°   | (typ.) |       | •     |  |

| D    | 9.8  |      | 10    | 0.385  |       | 0.393 |  |

| Е    | 5.8  |      | 6.2   | 0.228  |       | 0.244 |  |

| е    |      | 1.27 |       |        | 0.050 |       |  |

| e3   |      | 8.89 |       |        | 0.350 |       |  |

| F    | 3.8  |      | 4.0   | 0.149  |       | 0.157 |  |

| G    | 4.6  |      | 5.3   | 0.181  |       | 0.208 |  |

| L    | 0.5  |      | 1.27  | 0.019  |       | 0.050 |  |

| М    |      |      | 0.62  |        |       | 0.024 |  |

| S    |      |      | 8° (1 | max.)  |       |       |  |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

# © 2002 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.

© http://www.st.com